SC System

From NaplesPU Documentation

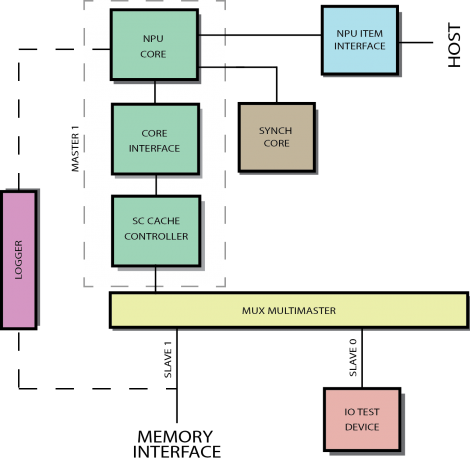

The NaplesPU single core system is defined in the npu_system.sv module, under src/sc/system folder. The following figure depicts the organization of the NaplesPU Single Core version:

The single core version instantiates the following modules:

- NaplesPU core: module

npu_core(described in NaplesPU core architecture) - item interface:

npu_item_interfacemodule allows host-device communication and performance info fetching. - transaction logger:

npu_core_loggermodule logs both incoming responses from the main memory and issued requests from the core to the memory. This module stores up to CORE_LOG_SIZE (default 512) for the core issued transactions, and MEM_LOG_SIZE (default 512) - core interface:

core_interfacemodule connects the NaplesPU core and the cache-controller for the single core version, modulesc_cache_controller - cache controller:

sc_cache_controllermodule, the cache controller for the single core version of the NaplesPU architecture, described in Cache Controller - system bus:

mux_multimastermodule, shared multi-master bus. It allows both the core and the host-interface to concurrently access the main memory and custom devices - test device:

io_device_testmodule, an example of a memory mapped custom device in the NaplesPU system - synchronization core:

synchronization_coremodule, acts as the synchronization master allowing thread synchronization through barriers. The module is the same as the many core version, although it requires minor adjustments:

assign network_available = 1'b1; assign ni_account_mess_valid = c2n_account_valid;

Since the single core version of the system has no network, the network availability input port has to be constantly high.