Difference between revisions of "Synchronization"

| Line 2: | Line 2: | ||

The nu+ manycore supports an hardware mechanism for Synchronization. The mechanism of synchronization is based on Barrier primitive. A barrier for a group of threads in the source code means any thread must stop at this point and cannot proceed until all other threads reach this barrier. | The nu+ manycore supports an hardware mechanism for Synchronization. The mechanism of synchronization is based on Barrier primitive. A barrier for a group of threads in the source code means any thread must stop at this point and cannot proceed until all other threads reach this barrier. | ||

| + | The mechanism of Barrier Synchronization implemented in this system is based on master-slave architecture, with master distributed on tiles. We support more independent barriers in parallel execution on manycore in each time. For identifying the different barriers we have an ID for each Barrier. Each Synchronization Core Master handles a range of Barrier in manycore. | ||

== Barrier Synchronization Protocol == | == Barrier Synchronization Protocol == | ||

| Line 10: | Line 11: | ||

In this protocol the ''Setup_Message'' and ''Account_Message'' are out-order and we use an enable bit for managing the Setup. | In this protocol the ''Setup_Message'' and ''Account_Message'' are out-order and we use an enable bit for managing the Setup. | ||

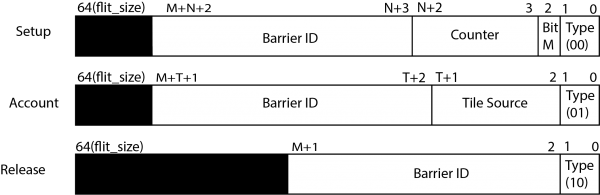

| − | The size of message change with number of Synchronization | + | The size of message change with number of Barrier Synchronization supported, as view in figure: |

| + | |||

[[File:SynchronizationMessages.png|600px]] | [[File:SynchronizationMessages.png|600px]] | ||

| + | |||

| + | The size of each message is of 1 flit (64 bit), and the field size of message change with number of Barrier supported. | ||

| + | We have these fields in the messages: | ||

| + | *'''Type''': It specifies the type of message: '00'(Setup_Message), '01'(Account_Message), '10'(Release_message). The size is 2 bits; | ||

| + | *'''Counter'''': It specifies the number of threads that takes part in the Barrier Synchronization; | ||

| + | *'''Barrier ID''': | ||

| + | *'''Tile Source''': | ||

| + | |||

=== Example of Barrier === | === Example of Barrier === | ||

Revision as of 12:00, 8 November 2017

Per Daniele

The nu+ manycore supports an hardware mechanism for Synchronization. The mechanism of synchronization is based on Barrier primitive. A barrier for a group of threads in the source code means any thread must stop at this point and cannot proceed until all other threads reach this barrier. The mechanism of Barrier Synchronization implemented in this system is based on master-slave architecture, with master distributed on tiles. We support more independent barriers in parallel execution on manycore in each time. For identifying the different barriers we have an ID for each Barrier. Each Synchronization Core Master handles a range of Barrier in manycore.

Contents

Barrier Synchronization Protocol

The Barrier protocol is based on a message passing. We have three type of message:

- Setup_Message: It configures the struct of Barrier in Synchronization Core;

- Account_Message: It notifies to Synchronization Core that the thread is arrived to point of Barrier;

- Release_Message: It notifies from Synchronization Core to Barrier Core that all threads are arrived to point of Synchronization, so the Barrier can end.

In this protocol the Setup_Message and Account_Message are out-order and we use an enable bit for managing the Setup. The size of message change with number of Barrier Synchronization supported, as view in figure:

The size of each message is of 1 flit (64 bit), and the field size of message change with number of Barrier supported. We have these fields in the messages:

- Type: It specifies the type of message: '00'(Setup_Message), '01'(Account_Message), '10'(Release_message). The size is 2 bits;

- Counter': It specifies the number of threads that takes part in the Barrier Synchronization;

- Barrier ID:

- Tile Source: