Difference between revisions of "System deployment"

| Line 4: | Line 4: | ||

[[File:Nexys4DDR.jpg|900px]] | [[File:Nexys4DDR.jpg|900px]] | ||

| + | |||

| + | The ''nuplus_system'' lays on the middle of the design, while ''uart_router'' and ''memory_controller'' translate nu+ transactions letting the system communicate with both the host (through the UART) and with the board memory (through the DDR interface). | ||

== Memory Controller == | == Memory Controller == | ||

Revision as of 18:26, 14 May 2019

TODO: descrizione uart_router, memory_controller, con riferimento a template nexys4ddr, (comandi, console) e memoria, disegno/schema, interazione con host, loading memoria, avvio kernel

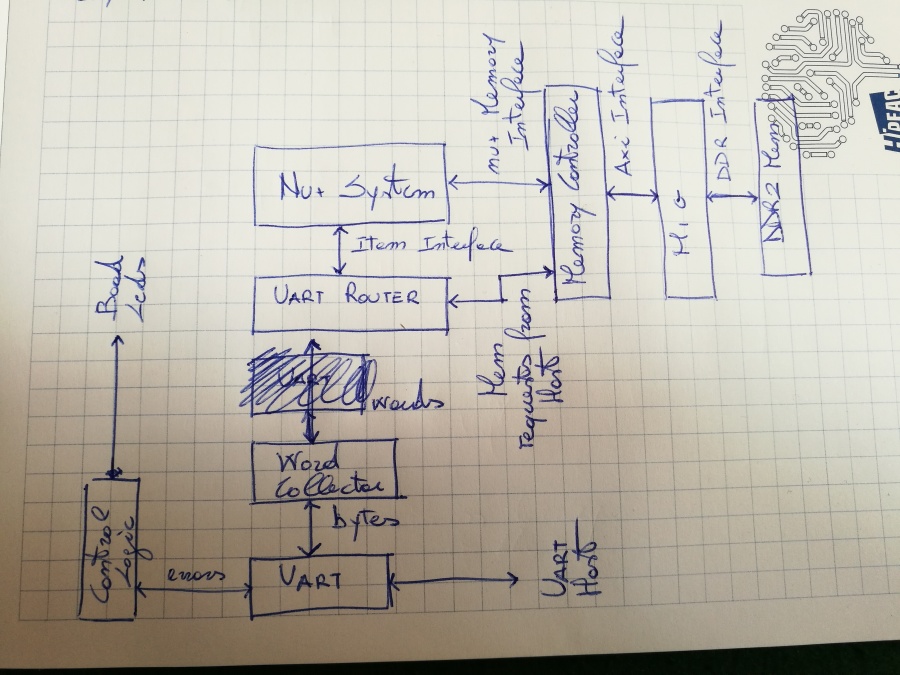

The SC_System has been deployed on a Nexys4DDR FPGA board, modules involved are located into boards/nexys4ddr and src/deploy/ folders. The design interconnects the board DDR memory and the UART respectively to the Memory and Item interfaces. The figure below shows a schematic block of the top module:

The nuplus_system lays on the middle of the design, while uart_router and memory_controller translate nu+ transactions letting the system communicate with both the host (through the UART) and with the board memory (through the DDR interface).

Memory Controller

da AXI a DDR

Host interaction

Uart controller e traduzione in items per nu+ (da uart_router)

Console commands

uart_loader.py