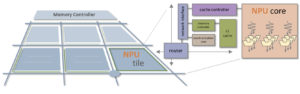

The Naples Processing Unit, dubbed NaplesPU or NPU, is a comprehensive open-source manycore accelerator, encompassing all the architecture layers from the compute core up to the on-chip interconnect, the coherence memory hierarchy, and the compilation toolchain.

Entirely written in System Verilog HDL, NaplesPU exploits the three forms of parallelism that you normally find in modern compute architectures, particularly in heterogeneous accelerators such as GPU devices: vector parallelism, hardware multithreading, and manycore organization. Equipped with a complete LLVM-based compiler targeting the NaplesPU vector ISA, our open-source project will let you experiment with all of the flavors of today’s manycore technologies.

These are the key ambitions of the NaplesPU project:

- be a reference open-source project featuring a fully fledged GPU-like processing system,

- provide a configurable and open platform for the design and evaluation of customized accelerators,

- offering free remote access to a powerful emulation platform, under negotiated conditions, in addition to the mere source code,

- become an unparalleled learning resource for students and practitioners who want to put their hands on the internals of a manycore architecture.